Setup time and Hold time are very important concepts when designing circuits. Compromising with these parameters would give an organized output. Whenever we see a circuit, we see it switching instantly ON and instantly OFF. It just appears like teleportation. Electronics from the low state were teleported to a higher state and vice versa. However, teleportation never occurs in electronics. No matter how fast switching circuits has been invented, it will always take some amount of time.

Switching a circuit from LOW to HIGH does involve time. The time involved is as small as nanoseconds or picoseconds.

Setup Time:

The minimum time required to keep the input data stable while the clock has started to change is called Setup Time. Any change or malfunction of data within this period leads to Setup Violations.

Hold Time:

The minimum time required to keep the input data stable after the clock transition has taken place is called Hold Time. Any change or malfunction of data within this period leads to Hold Violations.

Below is the image how the human eye perceives a change in the clock signal

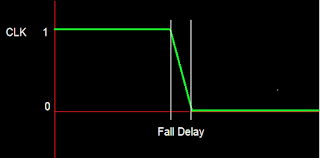

For the humans, it's always clear whether it is a HIGH or a LOW signal. However, the transition takes time. The delay introduced for the electronics to travel from a HIGH state to LOW takes place as shown in the below diagram.

The fall delay is the time taken for the transition from HIGH state to a LOW signal of any state. So when we see a clock working, we actually have a clock like this below.

To model these delays in Verilog, we use #NUMBER where NUMBER is the minimum number of clocks, the delay has to be made.

For example, if we make a simple code for AND gate, then the ideal gate would be coded as

and(C, A, B); This represents C = A & B

However, with a delay in the circuit, we can code it as

and #1 (C, A, B): This too represents C = A & B but the output would have a delay of 1 tick of the clock.

Now each diagram above is a digital representation of a signal. What happens in the analog form is the most interesting part of signals. The analog form of the signal is the reason for Setup time and Hold time. When a signal is flipped to its complementary state, it takes time to stabilize. Until that time, the electronics oscillates in an undamped manner. This is called the switch Bouncing Effect. The following diagram would explain clearly.

Thus, the output clock edge must be captured and stabilized before any data change occurs. Now in Verilog, we use @posedge or @negedge for most sequential circuits. This means that the data has to undergo certain operations and produce an output during that change of transition, neither before, nor after. So the data is "held tightly" while the clock is transiting from the LOW state as we cannot afford the data to change before edge just because of some quantum disturbances. Now, as soon as the clock reaches midway, the change in data takes place and is again "held together" until the clock stabilizes its HIGH state.

As shown in the above diagram, during stabilization of clock, there are several "minute" positive and negative edge caused by oscillations which might trigger a change in the data if not held properly. It is this, why we require Setup Time and Hold Time.

To practice this in Verilog, we will execute some basic modules.

Code:

module Delay(A, B, C, D, E);

input A,B;

output C, D, E;

wire p, q;

or #50 an2(q, A, B);

or #52 an3(p, A, B);

nand #54 an4(E, A, B);

assign C = p;

assign D = q;

endmodule

TestBench:

module TEst1;

reg A,B;

wire C,D,E;

Delay DEF(A, B, C, D, E);

initial begin

A = 1;

B = 0;

end

endmodule

OUTPUT with the delay for all changes

Here is an easy example to explain Rise delay.

Code:

module Delay(A, B, C, D, E);

input A,B;

output C, D, E;

wire p, q;

or #2 an2(C, A, B);

or an3(D, A, B);

endmodule

TestBench:

module TEst1;

reg A,B;

wire C,D,E;

Delay DEF(A, B, C, D, E);

initial begin

A = 1;

B = 0;

fork

#10 A = 0; #B = 0;

end

endmodule

The signal D is driven without delay, hence it started the very moment, we started our simulation. It also changed its output when the inputs were changed at 10ns.

The signal C is driven by a delay of 2ns, hence it started with a delay of 2ns and also ended with a delay of 2ns. #NUM defines the delay where NUM is the delay of every parameter.

Now let us introduce, Rise delay and Fall delay. Its basic syntax is:

#(R_Delay, F_Delay)

An example explaining both of these delay with comparison of no delay signal

Code:

module Delay(A, B, C, D, E);

input A,B;

output C, D, E;

wire p, q;

or an2(q, A, B);

or #(2,0) an3(p, A, B);

or #(0,2) an4(E, A, B);

assign C = p;

assign D = q;

endmodule

TestBench:

module TEst1;

reg A,B;

wire C,D,E;

Delay DEF(A, B, C, D, E);

initial begin

A = 1;

B = 0;

fork

#10 A = 0;

#10 B = 0;

join

end

endmodule

Output:

Now as shown in the code, signal C has a Rise delay of 2ns but no fall delay, hence it started at 2ns and not at 0ns but ended exactly at 10ns as we changed the signal exactly at 10ns. Thus without Fall delay, we didn't see the delay in C when the inputs were changed. The signal D, as usual, is having no delay hence it started and stopped without any delay. Signal E has no Rise delay, hence it started without any delay but it does have Fall delay, hence it ended with a delay of 2ns.

In the case of Turn Off delay, it is the minimum amount of time required to jump from X, 0, 1 to a high impedance state Z. Z is called the high impedance state. It signifies a connection split, hence the output has a very high resistance and is floating. Similarly, x signal has an unknown signal state.

Now, every signal has 3 delays with 3 sub delay for each delay. Confused? Me too.

We have

1.) Rise Delay 2.) Fall Delay 3.) Turn Off Delay

Within the Rise/ fall/ turn-off delay, we have 3 subcategories.

- Minimum Delay: This signifies the minimum amount of time delay to rise/ fall/ turn-off.

- Typical Delay: This signifies the typical amount of time delay to rise/ fall/ turn-off.

- Maximum Delay: This signifies the maximum amount of time delay to rise/ fall/ turn-off.

So now, we have to declare delay as follows:

#(min:typ:max, min:typ:max, min:typ:max)

Here is an example signifying the above:

Code:

module Delay(A, B, C, D, E);

input A,B;

output C, D, E;

wire p, q;

or an2(q, A, B);

or #(0:2:4,2:3:4,1:2:3) an3(p, A, B);

or #(2:6:7) an4(E, A, B);

assign C = p;

assign D = q;

endmodule

TestBench:

module TEst1;

reg A,B;

wire C,D,E;

Delay DEF(A, B, C, D, E);

initial begin

A = 1;

B = 0;

fork

#10 A = 0;

#10 B = 0;

join

end

endmodule

Output:

Here signal C is having a typical Rise delay of 2ns and typical Fall delay of 3ns.

No comments:

Post a Comment